|

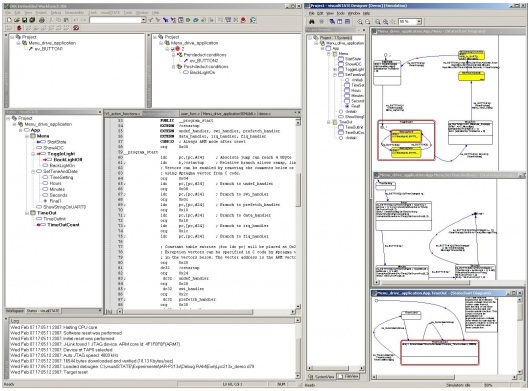

visualSTATE是一套精致、易用的开发工具,包含图形设计器、测试工具包,代码生成器和文档生成器,用于设计、测试和实现基于状态图设计的嵌入式应用。该款工具提供了先进的验证和测试模块,可以产生100%与您系统设计一致的紧凑C/C++代码,并可以在任何8位、16位、32位架构上运行。此外,它革命性地与 IAR Embedded Workbench C/C++编译调试环境无缝集成,能够真正做到基于硬件去调试状态机模型,并以直观的图形方式反馈出各个设计层面的详细信息。

自动系统分析和测试:

-

先进的规范性验证用于检查系统的逻辑一致性,以及鉴别出系统设计漏洞或错误,比如:

-

局部或系统死锁状态

-

不可到达状态或状态组合

-

强行状态激活动作和相互冲突的转换

-

带有歧义性行为的系统

-

模拟两可的系统定义

-

强大的测试功能,用于静态和动态系统分析

-

交互式的模拟仿真,包括图形动画和使用条件断点,用于测试系统的功能性

-

通过记录和播放测试序列,进行自动模拟

-

自动分析测试日志,获得模型的测试覆盖率

-

回放测试序列,进行回归测试

-

通过CSPYLink或RealLink对目标器件进行全面的图形化状态机调试,并支持多种硬件调试接口,例如J-Link、通用JTAG仿真器、NEXUS仿真器等。

集成性和兼容性:

-

易于与几乎任何GUI builder工具生成的代码相结合,为最终的应用创建模型

-

通过状态机模拟器直接与Altia设计相连,无需为原型开发编写任何GUI代码

-

易于集成到任何RTOS上,但不依赖任何一种OS服务

-

在某些场合下可以使用并行状态机范例,甚至不再需要简单的任务切换OS。

-

与IAR Embedded Workbench 开发环境紧密结合,支持特定目标和特定编译器的存储属性和关键字

-

代码兼容于所有的ANSI C编译器以及大多数调试工具和仿真器 用户获益之处

-

只需关注高级层面的状态机系统设计,无须操心底层软件的实现细节;

-

从设计工作的最初阶段起,就能着手确认设计是否符合要求;

-

在规范性验证器的帮助下找到潜在的软件漏洞,而不是等到验收阶段或者在客户现场才发现这些问题;

-

C-SPY中能在抽象层面图形化地调试复杂情形,另外还允许在状态机设计层面设置断点;

-

由于该软件生成的代码量很少,用户就可以选用RAM和ROM资源较小的目标器件,从而节约了单位成本;

-

使用户在更短的时间内,以更高的质量将产品投入市场。

重要特性:

-

基于统一建模语言(UML)状态机理论的图形化模型设计;

-

对设计模型进行规范性验证,检查系统的逻辑一致性,鉴别出系统设计漏洞或错误;

-

设计过程的早期阶段,甚至在硬件设计尚未完成之前,就可以使用测试工具来确保应用能按照预想方式运行;

-

自动代码生成功能可以生成极为紧凑的C/C++代码,100%与设计保持一致;

-

自动文档生成功能提供了详尽的信息;

-

与IAR Embedded Workbench 无缝集成,提供多种微控制器和评估板的现成示例代码;

-

通过CSPYLink或RealLink对目标器件进行综合的图形化状态机调试;

-

支持多种硬件调试接口,例如J-Link、通用JTAG仿真器、NEXUS仿真器等。

应用领域

对于处理复杂性不断增加的整体或部分基于状态和响应的应用,visualSTATE是一款极好的管理工具。 无论层次结构有多么复杂,只要是能用状态机描述的问题都能采用visualSTATE进行设计。

测试和验证工具确保了设计质量。主要应用领域有:

-

生命科学应用和个人医疗仪器

-

需要人机交互功能的应用,比如多媒体播放器,家用电器等。

-

工业自动化,包括楼宇自动化

-

汽车应用,如车身控制

-

所有需要考虑RAM和ROM使用量,具有高质量和高完整需求的应用

|