ModelSim是业界最优秀的语言仿真器,它提供最友好的调试环境,是FPGA设计的RTL级和门级电路仿真的首选。它支持PC和UNIX、LINUX平台,是唯一的单一内核支持VHDL和Verilog混合仿真的仿真器。它采用直接优化的编译技术、Tcl/Tk技术、和单一内核仿真,编译仿真速度业界最快,编译的代码与平台无关,便于保护IP核,具有个性化的图形界面和用户接口,为用户加快调试提供强有力的手段。全面支持VHDL和Verilog语言的IEEE 标准,以及IEEE VITAL 1076.4-95 标准,支持C语言功能调用, C的模型,基于SWIFT的SmartModel逻辑模型和硬件模型。

主要特点:

-

采用直接编译结构,编译仿真速度最快;

-

单一内核无缝地进行VHDL和Verilog混合仿真;

-

与机器和版本无关,便于数据移植和库维护;

-

与机器无关的编译代码便于保护和利用IP;

-

简单易用和丰富的图形用户界面,快速全面调试;

-

Tcl/Tk用户可定制仿真器;

-

完全支持VHDL/Verilog国际标准,完全支持Verilog 2001;首家支持SystemC

-

支持众多的ASIC和FPGA厂家库;

-

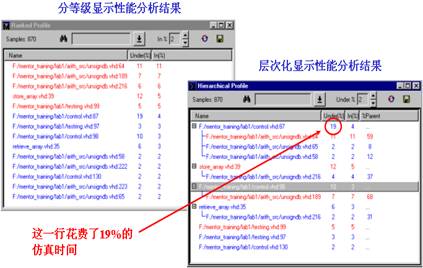

集成的Performance analyzer帮助分析性能瓶颈,加速仿真;

-

加强的代码覆盖率功能Code coverage,能报告出每个分支的执行情况,进一步提高了测试的完整性;

-

同一波形窗口可以显示多组波形,并且能进行多种模式的波形比较(Wave Compare);

-

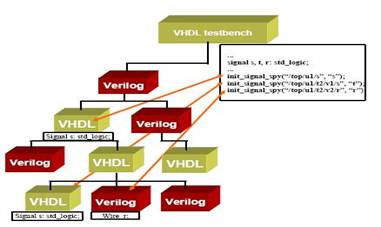

先进的Signal Spy功能,可以方便地访问VHDL 或者 VHDL 和Verilog 混合设计中的下层模块的信号,便于设计调试;

-

支持加密IP;

-

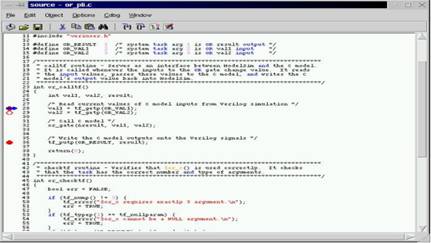

集成的C调试器,支持用C 语言完成测试平台和模块;

-

支持64位的OS

ModelSim的调试功能是其被人称道的重要特点,现列举一些高级调试手段如下:

Ø Dataflow数据流窗口

ModelSim的Dataflow窗口提供了一个图形化的设计查看和调试手段。通过内嵌的可视化跟踪引擎,使用者能够快速的遍历整个设计,追踪到设计中的问题。在任意节点通过简单的点击鼠标的按钮,与节点相关的所有逻辑连接都能被立即显示出来。因为Dataflow窗口与ModelSim的其他窗口交叉链接,你能实时的将逻辑图中的任何位置节点所对应的源代码行在source窗口标识出来。Dataflow窗口与Wave窗口(波形窗口)中处于活动状态的光标同样是实时互动的,用户能够在Wave窗口中沿着仿真时间坐标任意移动光标,然后实时地观察Dataflow窗口中的逻辑连接图中所标注的逻辑值。另一个特性“ChaseX”能够自动地追踪当前逻辑值为不定态“X”的节点的“X”产生源,并完整地显示出从“X”产生源到当前节点的逻辑路径图。拥有了Dataflow所提供的这些强大的调试手段,将极大地缩短您在设计调试阶段发现和修正Bug的时间。

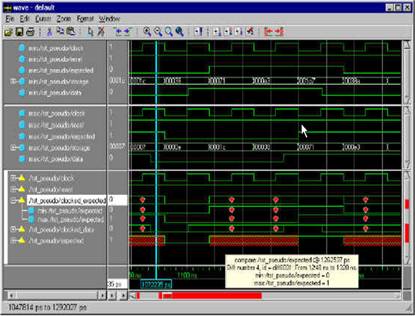

Ø 波形比较

波形比较让您快速精确地验证仿真结果,使用非常方便。测试信号和参考信号在同一界面下进行比较,不同之处用红色高亮标记。可进行连续的或定时的比较。可以选择正在进行的仿真和保存好的仿真结果进行比较,也可调用两个保存过的结果进行比较。

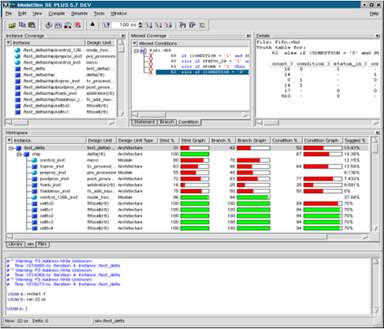

Ø 代码覆盖率

代码覆盖率分析功能帮助设计者迅速地编写出更完善的,强大的测试向量,并且帮助设计者确认是否设计中所有的部分都已经被测试向量测试到了。代码覆盖率分析在模块测试或是系统级测试的全芯片层次都能够实施。

ModelSim的代码覆盖率分析给设计者提供了许多的基于模块的覆盖率分析手段。其中行覆盖率检查能够报告出代码中的哪一行没有被测试到。分支覆盖率检查则能够报告出设计中大量的条件选择类型语句的执行情况,哪些条件被测试到了,哪些条件没有被当前测试向量测试到。所有这些各种覆盖率的统计报告都能够在图形化的窗口显示出来,并且能够在源代码窗口中把相关语句标识出来。ModelSim的代码覆盖率功能集成在了内核中,因而优化了仿真性能,而且使用者无需任何额外的工作即可快速的进行代码覆盖率的分析。

Ø 性能分析

性能分析帮助设计者快速识别性能瓶颈。指出无效代码,并分析每一段有效代码的执行时间和比例,分析哪一段代码的效率低。性能分析功能可对行为级、RTL级和门级进行分析。

Ø 信号侦测(Signal Spy)

从设计的任何点,Signal Spy功能允许你去定位,观察,驱动,强制赋值和释放信号以及位于层次化的VHDL或是混合语言设计中的底层信号线。在ModelSim的环境中,无需对设计者现有的代码进行丝毫改动,就能轻松实现这个功能。在测试向量的设计当中,这个功能是非常有用的。

Ø C语言的调试

ModelSim不仅支持C语言的仿真,更能进行C语言的调试,支持C语言的测试向量和模型,在同一仿真中对PLI和FLI调试。并支持断点设置跟踪等调试手段。

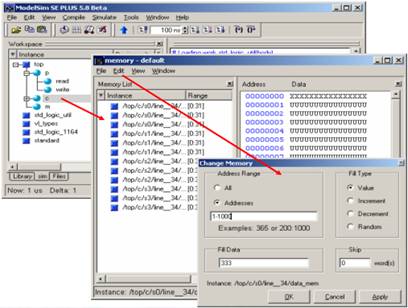

Ø Memory窗口

自动提取,实时查看Memory中每个地址的内容

Ø 其他还具有如IP集成、对于仿真状态的仿真和恢复,继续仿真等功能

|